|

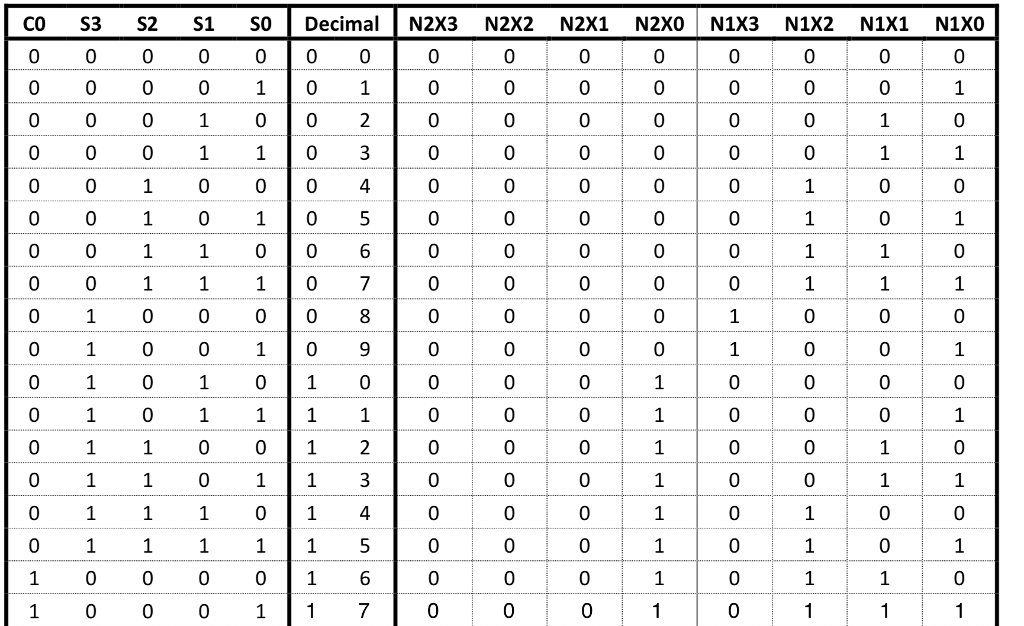

3/17/2024 0 Comments Verilog decimal hex binary The code snippet below shows this general syntax. We use the same syntax to declare a variable in verilog, regardless of the exact type. These four different values are shown in the table below. Regardless of the exact type we are using, there are four valid values we can assign to individual bits in our data. These types can store data, meaning that their behaviour is similar to variables in other programming languages such as C. We primarily use the variable types to model registers or flip flops in our design. They are unable to store values on their own and must be driven with data. We use the net types to model connections in our digital circuits. We use these two different groups to model different elements of our digital circuits. The code snippet below shows the general syntax for representing digital data in verilog.īroadly speaking, the basic data types in verilog can be split into two main groups - net types and variable types. Therefore, we can create data busses which contain as many bits as we choose.

This is because we are fundamentally describing hardware circuits when we use verilog. Unlike in other programming languages, we also need to define the number of bits we have in our data representation. We can express this data as either a binary, hexadecimal or octal value. When we write verilog, we often need to represent digital data values in our code. As a result, there is often no need necessary to explicitly perform type conversions in verilog. When we assign data to a signal in verilog, the data is implicitly converted to the correct type in most cases. We can also use types which interpret our data as if it were a numeric value.

We can use types which interpret data purely as logical values, for example. The type which we specify is used to define the characteristics of our data. This includes a discussion of data respresentation, net types, variables types, vectors types and arrays.Īlthough verilog is considered to be a loosely typed language, we must still declare a data type for every port or signal in our verilog design. In this post, we talk about the most commonly used data types in Verilog.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed